Product Summary

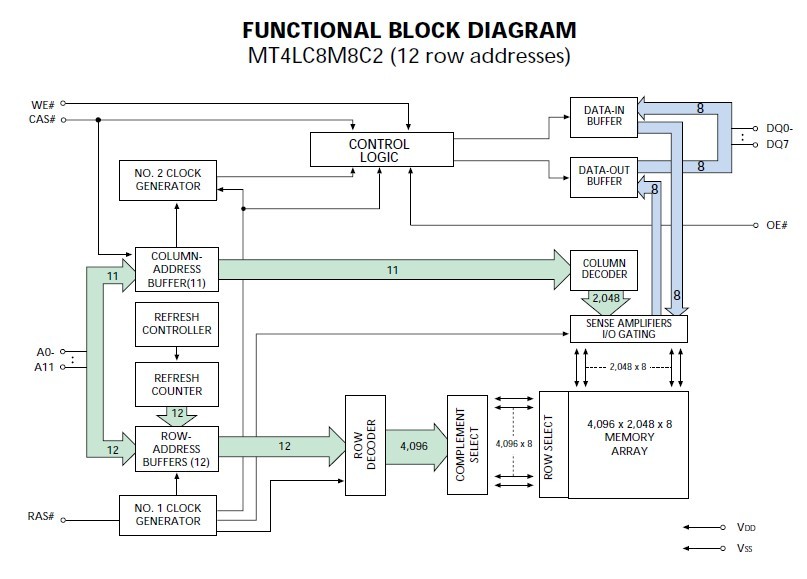

The MT4LC8M8C2TG5 is a high-speed CMOS, dynamic random-access memory device containing 67,108,864 bits and designed to operate from 3V to 3.6V. The MT4LC8M8C2TG5 is functionally organized as 8,388,608 locations containing eight bits each. The 8,388,608 memory locations are arranged in 4,096 rows by 2,048 columns on the C2 version and 8,192 rows by 1,024 columns on the P4 version.

Parametrics

MT4LC8M8C2TG5 absolute maxing ratings: (1)Voltage on VCC Relative to VSS: -1V to +4.6V; (2)Voltage on NC, Inputs or I/O Pins Relative to VSS: -1V to +4.6V; (3)Operating Temperature, TA (ambient): 0℃ to +70℃; (4)Storage Temperature (plastic): -55℃ to +150℃; (5)Power Dissipation: 1W.

Features

MT4LC8M8C2TG5 features: (1)Single +3.3V ±0.3V power supply; (2)Industry-standard x8 pinout, timing, functions, and packages; (3)12 row, 11 column addresses (C2) or 13 row, 10 column addresses (P4); (4)High-performance CMOS silicon-gate process; (5)All inputs, outputs and clocks are LVTTLcompatible; (6)Extended Data-Out (EDO) PAGE MODE access; (7)4,096-cycle CAS-BEFORE-RAS (CBR) REFRESH distributed across 64ms; (8)Optional self refresh (S) for low-power data retention.

Diagrams

|

MT4LC16M4A7 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT4LC16M4G3 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT4LC16M4H9 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT4LC16M4T8 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT4LC1M16C3 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT4LC1M16E5 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))